RISC-V Multistage Pipelined CPU

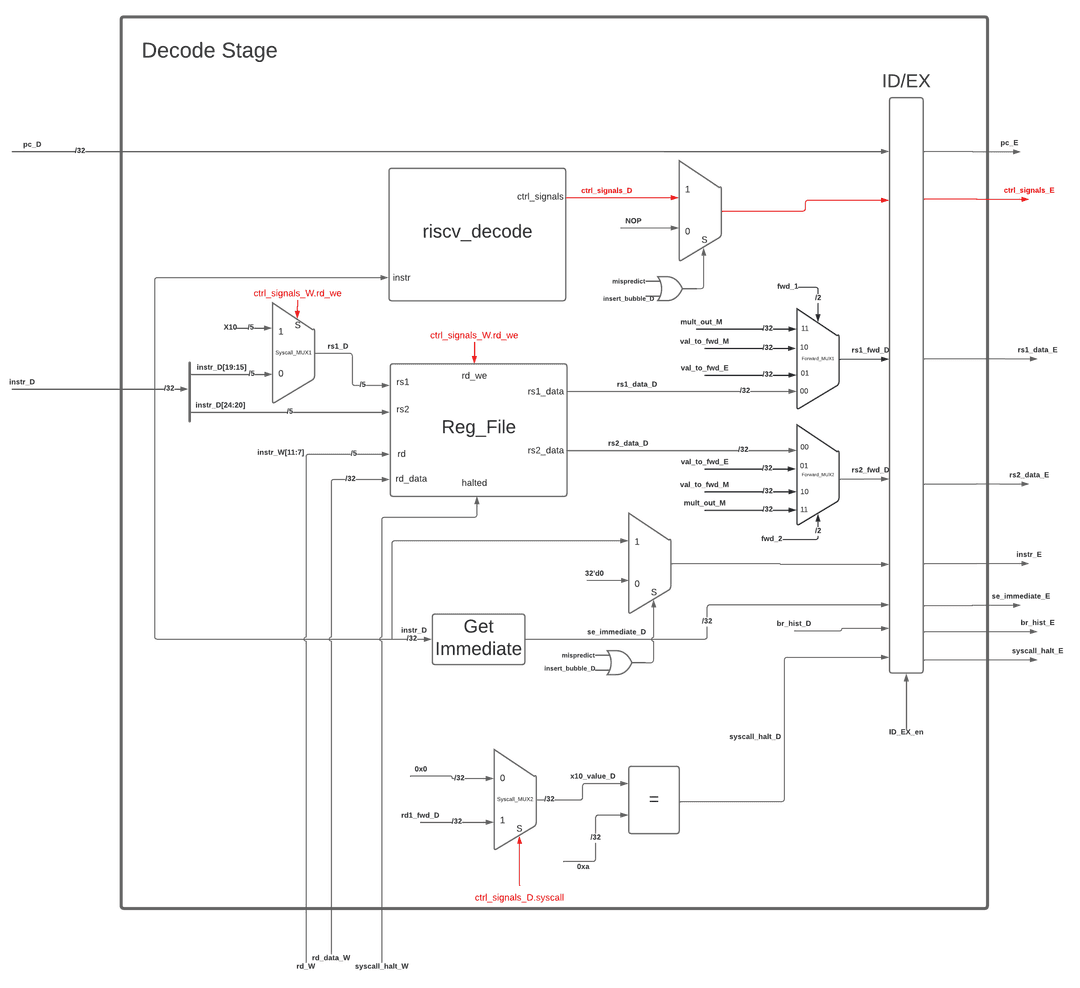

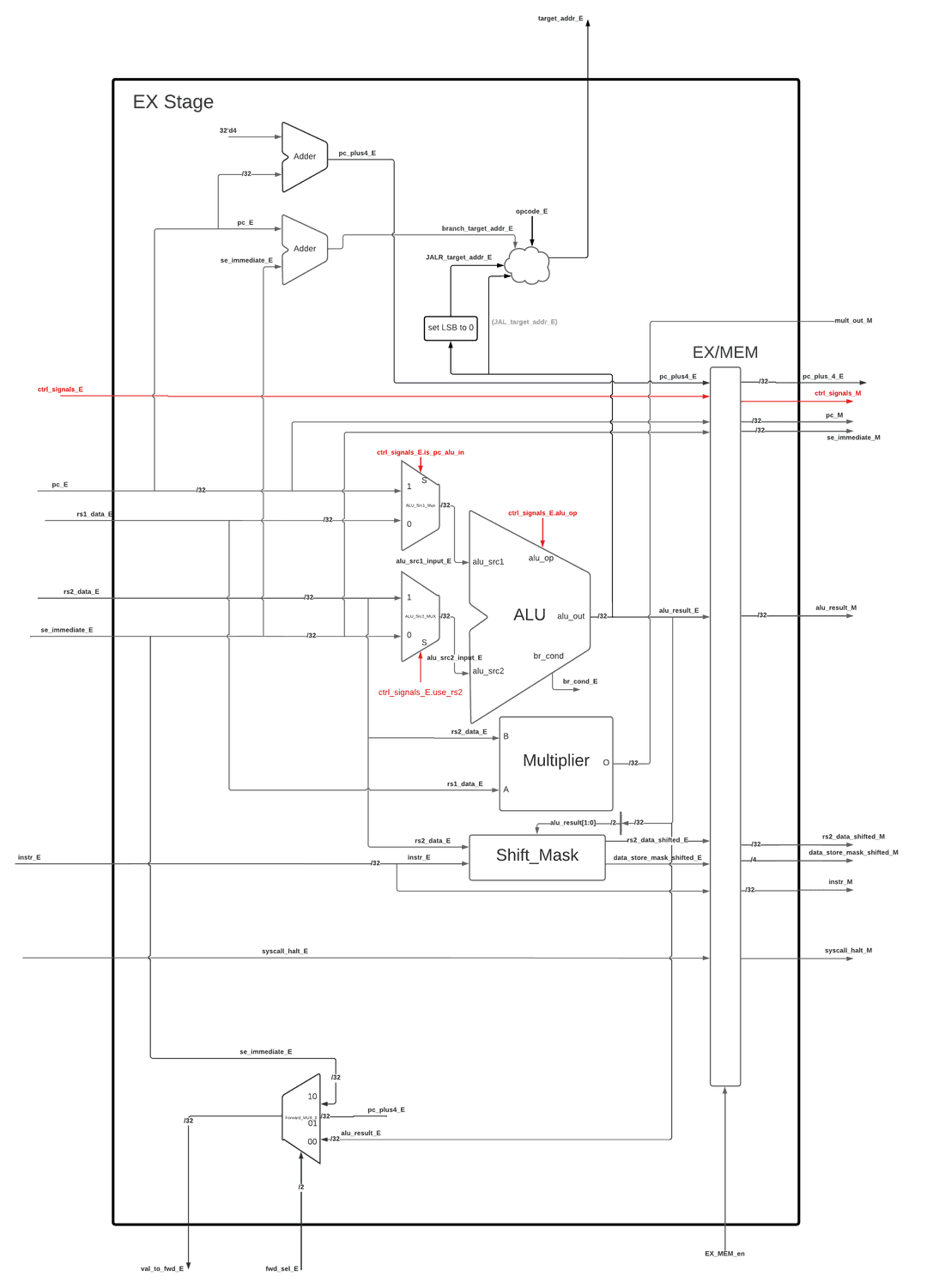

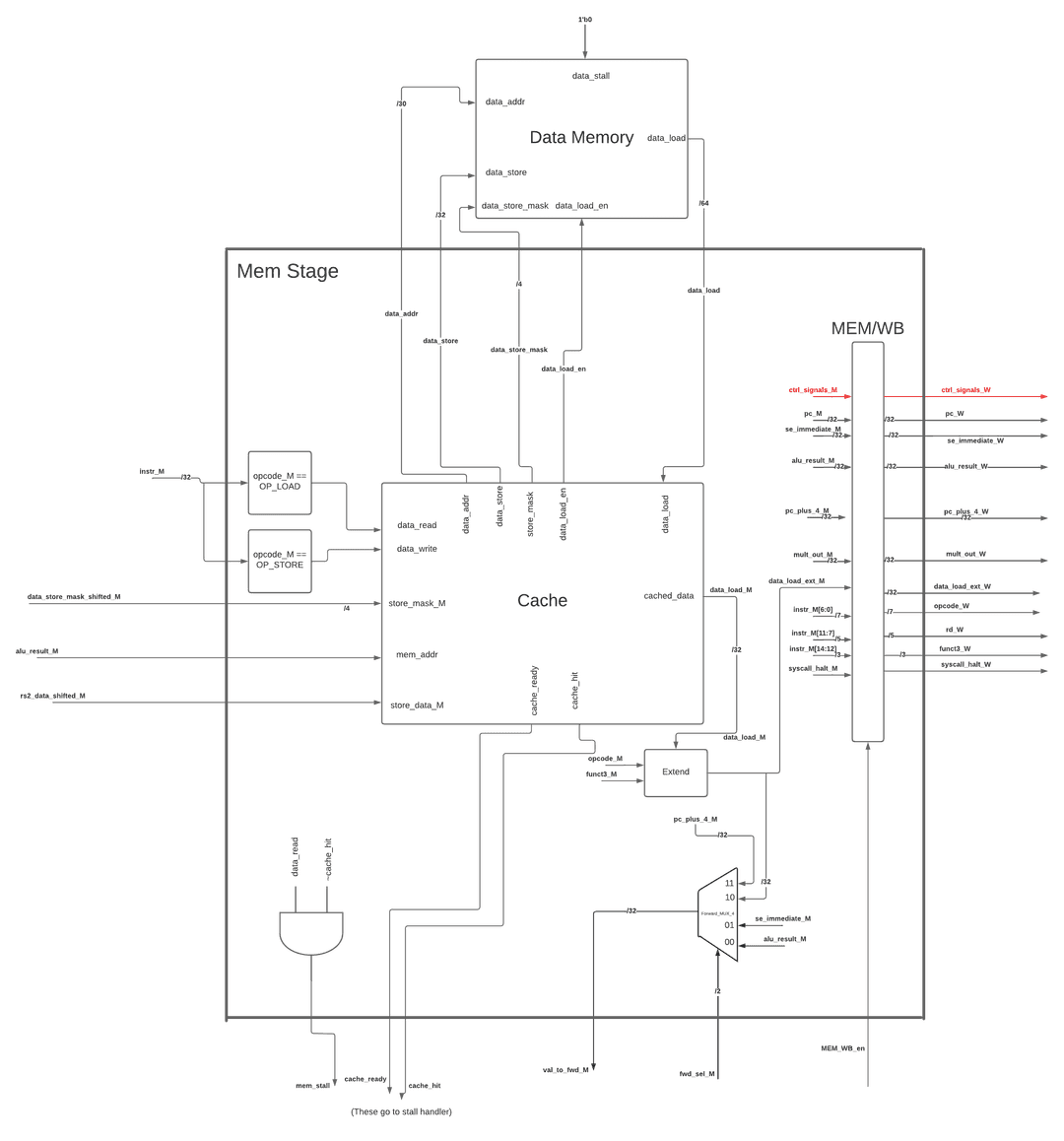

This 5-stage pipelined CPU supports the RV32I RISC-V instruction set architecture (ISA). The processor also includes RAW hazard detection, branch prediction, and a direct-mapped cache (see MEM stage). The main bottlenecks are the cache miss rate and the BTB miss rate, both of which necessitate processor stalls (incurring instruction delays).

Tests included:

- - Mixed program (programs with poor functional locality)

- - Matrix multiplication (no optimization)

- - Matrix multiplication (-O3 compiler optimization)

[source code]